Hệ thống phần cứng ở mức cao

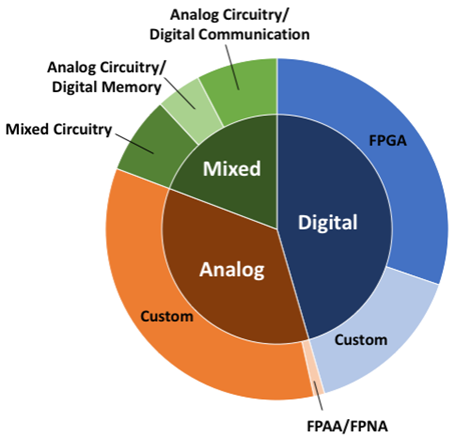

Hệ thống phần cứng ở mức cao được chia thành các triển khai mạch tương tự, mạch số hoặc mạch hỗn hợp tương tự-số như Hình 1. Trước khi đi sâu vào các hệ thống neuromorphic, cần lưu ý đặc điểm chính của các hệ thống mạch tương tự và mạch số, và cách chúng liên hệ đến các hệ thống neuromorphic. Hệ thống mạch tương tự sử dụng đặc tính vật lý gốc của các linh kiện điện tử như một phần quá trình tính toán của hệ thống, trong khi hệ thống mạch số có xu hướng dựa vào các cổng logic với đại số Boolean, chẳng hạn như cổng AND, OR và NOT, để hình thành tính toán. Bộ não sinh học là một hệ thống tương tự và dựa vào các đặc tính vật lý để tính toán chứ không dựa trên logic của phép tính Boolean. Nhiều tính toán trong phần cứng neuromorphic cho phép các kiểu hoạt động ở đó các hệ thống mạch tương tự thực hiện một cách tự nhiên. Hệ thống mạch số dựa trên giá trị rời rạc trong khi hệ thống mạch tương tự xử lý giá trị liên tục. Hệ thống mạch số thường đồng bộ hoặc dựa trên xung clock, trong khi hệ thống mạch tương tự thường bất đồng bộ; tuy nhiên, trong neuromorphic, quy tắc này thường không đúng, vì ngay cả các hệ thống mạch số cũng có xu hướng hướng sự kiện và các hệ thống tương tự đôi khi sử dụng xung clock để đồng bộ hóa. Hệ thống mạch tương tự dễ nhiễm nhiễu hơn so với hệ thống mạch số; tuy nhiên, đã có một số lập luận rằng bởi vì mạng nơ-ron có thể chống lại nhiễu và lỗi, nên chúng có thể là ứng cử viên lý tưởng cho việc triển khai trên mạch tương tự.

Khi thiết kế một hệ thống neuromorphic lớn, những thách thức bắt nguồn từ việc cố gắng tạo ra một hệ thống có số lượng lớn các tế bào thần kinh và synapse tương tự như bộ não bằng công nghệ bán dẫn. Có những xu hướng nghiên cứu về cách các thiết kế phần cứng neuromorphic khác nhau xử lý giao tiếp các xung tăng vọt hoặc tăng vọt (spikes) giữa các tế bào thần kinh. Các nghiên cứu về tính toán neuromorphic và SNN đã được thực hiện bởi các tổ chức/nhóm nghiên cứu sau:

- Akida Brain Chip

- Neurogrid & BrainDrop (Đại học Stanford)

- BrainScaleS and Spinnaker (Human Brain Project)

- TrueNorth (IBM)

- LOIHI

- DYNAPs

- Darwin

i. Mạch số

Các linh kiện FPGA thường được sử dụng để tối ưu hóa trong các hệ thống neuromorphic. Việc sử dụng FPGA thường được tối ưu hóa như một giải pháp trung gian trong việc triển khai trên chip. Trong trường hợp này, khả năng lập trình của FPGA không được tối ưu hóa như một phần của quá trình triển khai neuromorphic; nó chỉ đơn giản được sử dụng để lập trình FPGA như một hệ thống neuromorphic, rồi được đánh giá sau đó. Tuy nhiên, cũng thường xảy ra trường hợp FPGA được sử dụng làm phần triển khai cuối cùng; và trong trường hợp này, khả năng lập trình của thiết bị có thể được tận dụng để thực hiện các giao thức, mô hình và thuật toán mạng một cách cơ bản. Do tính phổ biến tương đối của chúng, hầu hết các nhà nghiên cứu đều có thể triển khai hệ thống trên một linh kiện FPGA với các ngôn ngữ mô tả phần cứng như VHDL hoặc Verilog để triển khai thành các mạch trong FPGA. Nếu mục tiêu của việc phát triển một hệ thống neuromorphic là để đạt được tốc độ nhanh hơn so với mô phỏng trên phần mềm, thì FPGA là một lựa chọn tốt. Tuy nhiên, nếu mục tiêu là đạt được một hệ thống nhỏ, công suất thấp thì FPGA có lẽ không phải là cách tiếp cận chính xác. Một số ưu điểm của FPGA so với việc triển khai vi mạch số và tương tự đó là thời gian thiết kế và chế tạo ngắn hơn, khả năng cấu hình lại và khả năng tái sử dụng cho các ứng dụng khác nhau, tối ưu hóa cho từng bài toán và giao tiếp dễ dàng với máy tính chủ.

Các chip mạch tích hợp chuyên dụng hay full-custom (ASIC) cũng rất phổ biến cho việc thực hiện neuromorphic [2, 3]. IBM’s TrueNorth, một trong những sản phẩm thực hiện neuromorphic phổ biến nhất hiện nay, là một thiết kế ASIC tùy chỉnh đầy đủ [4 – 6]. Chip TrueNorth bất đồng bộ một phần và đồng bộ một phần, trong đó một số hoạt động không xảy ra với xung clock, nhưng xung clock dùng để điều chỉnh bước thời gian cơ bản trong hệ thống. Một lõi trong hệ thống TrueNorth chứa cấu hình mảng thanh ngang 256×256 ánh xạ xung tăng vọt nhận được tới các nơ-ron. Hành vi của hệ thống là xác định, nhưng có khả năng tạo ra hành vi ngẫu nhiên thông qua nguồn giả ngẫu nhiên. Tính ngẫu nhiên này có thể được sao chép chính xác trong một mô phỏng phần mềm.

SpiNNaker, một triển khai neuromorphic phổ biến khác, là một hệ thống song song, mạch số tùy chỉnh đầy đủ [7, 8]. SpiNNaker bao gồm nhiều lõi số nguyên nhỏ và một cơ chế giao tiếp kết nối liên kết tùy chỉnh được tối ưu hóa cho hành vi giao tiếp của kiến trúc mạng dựa trên xung tăng vọt. Đó là kết cấu giao tiếp nhằm xử lý một số lượng lớn các thông điệp rất nhỏ. Bản thân đơn vị xử lý rất linh hoạt và không tùy chỉnh cho neuromorphic, nhưng cấu hình của mỗi chip SpiNNaker bao gồm lệnh và bộ nhớ dữ liệu để giảm thiểu thời gian truy cập cho dữ liệu được sử dụng thường xuyên. Giống như TrueNorth, SpiNNaker hỗ trợ phân tầng các chip để tạo thành các hệ thống lớn hơn. TrueNorth và SpiNNaker cung cấp các ví dụ điển hình về các điểm cực đoan mà người ta có thể thực hiện với việc triển khai phần cứng trên mạch số. TrueNorth đã chọn mô hình SNN cố định với các nơ-ron mô hình Integrate-and-Fire và kết nối có thể lập trình hạn chế và không có tính năng học trên chip. Nó được tối ưu hóa cao cho mô hình đã chọn và giao thức của mạng. Mặt khác, SpiNNaker cực kỳ linh hoạt trong mô hình nơ-ron đã chọn, mô hình synapse và thuật toán học tập. Tất cả các tính năng và giao thức của mạng cực kỳ linh hoạt. Tuy nhiên, sự linh hoạt này đi kèm với chi phí hiệu quả năng lượng. Theo báo cáo của Furber [9], TrueNorth tiêu thụ 25 pJ cho mỗi kết nối, trong khi SpiNNaker tiêu thụ 10 nJ cho mỗi kết nối.

ii. Mạch tương tự

Tương tự như việc phân tích các hệ thống dựa trên mạch số, chúng ta tách các hệ thống mạch tương tự thành các triển khai trên chip có thể lập trình và tùy chỉnh. Vì có FPGA cho các hệ thống mạch số, nên cũng có các linh kiện analog khả trình FPAA (Field Programmable Analog Array). Vì nhiều lý do tương tự mà FPGA đã được sử dụng để triển khai neuromorphic dạng mạch số, nên FPAA cũng đã được sử dụng [10, 11]. Cũng đã có những linh kiện FPAA custom được phát triển đặc biệt cho các hệ thống neuromorphic, bao gồm linh kiện khả trình nơ-ron (FPNA – Field Programmable Neuron Array) [12] và NeuroFPAA [13]. Các mạch này chứa các thành phần có thể lập trình cho tế bào thần kinh, synapse và các thành phần khác, hơn là sử dụng linh kiện FPAA vốn mang tính phổ quát hơn cho các thiết kế mạch tương tự chung.

Người ta đã chỉ ra rằng các vi mạch tích hợp tương tự và các hệ thống neuromorphic có một số đặc điểm khiến chúng rất phù hợp với nhau. Đặc biệt, các yếu tố như bảo toàn điện tích, khuếch đại, ngưỡng và tích phân đều là những đặc điểm có trong cả hệ thống mạch tương tự và hệ thống sinh học [14]. Một trong những cách tiếp cận phổ biến đối với các hệ thống neuromorphic tương tự là sử dụng mạch hoạt động ở chế độ dưới ngưỡng, thường cho mục đích sử dụng năng lượng hiệu quả [15, 16].

iii. Mạch hỗn hợp tương tự-số

Các hệ thống mạch hỗn hợp tương tự-số cũng rất phổ biến đối với các hệ thống neuromorphic [17, 18]. Do tính chất tự nhiên của nó tương tự hệ thống sinh học, mạch tương tự đã được sử dụng phổ biến trong các hệ cấu trúc neuromorphic mạch hỗn hợp tương tự-số để thực hiện các thành phần xử lý của nơ-ron và synapse. Tuy nhiên, có một số vấn đề với hệ thống mạch tương tự có thể được khắc phục bằng cách sử dụng các thành phần mạch số, bao gồm cả sự không tin cậy.

Trong một số hệ thống neuromorphic, đã xảy ra trường hợp các giá trị trọng số synapse hoặc một số thành phần của bộ nhớ của hệ thống được lưu trữ bằng cách sử dụng các thành phần mạch số, có thể ít nhiễu hơn và đáng tin cậy hơn so với các thành phần bộ nhớ dựa trên mạch tương tự. Ví dụ, trọng số synapse thường được lưu trữ trong bộ nhớ mạch số cho các hệ thống neuromorphic tương tự. Các nền tảng neuromorphic khác chủ yếu là mạch tương tự, nhưng sử dụng giao tiếp kỹ thuật mạch số, bên trong chip, đến và đi từ chip, hoặc giữa các chip neuromorphic [19, 20]. Giao tiếp bên trong và giữa các chip neuromorphic thường ở dạng các xung số cho các triển khai này. Việc sử dụng các thành phần mạch số cho khả năng lập trình hoặc cơ chế học tập cũng đã phổ biến trong các hệ thống mạch hỗn hợp tương tự-số [21, 22].

Hai dự án lớn trong thiết kế mạch hỗn hợp tương tự-số là Neurogrid và BrainScaleS. Neurogrid – chip chủ yếu là mạch tương tự, có lẽ gần giống nhất với định nghĩa ban đầu của neuromorphic do Mead đưa ra [23]. Cả hai cách triển khai này đều nằm trong thiết kế hỗn hợp tương tự-số vì trong khuôn khổ giao tiếp truyền thông số. BrainScaleS là một triển khai mức wafer có các thành phần mạch tương tự [24]. Neurogrid hoạt động ở chế độ dưới ngưỡng (subthreshold) và BrainScaleS hoạt động ở chế độ siêu ngưỡng (super-threshold). Các nhà phát triển của BrainScaleS đã chọn chế độ siêu ngưỡng vì nó cho phép chip BrainScaleS hoạt động với tốc độ cao hơn nhiều so với của Neurogrid, đạt được tốc độ tăng gấp 10.000 lần [9].

Các thành phần ở mức linh kiện

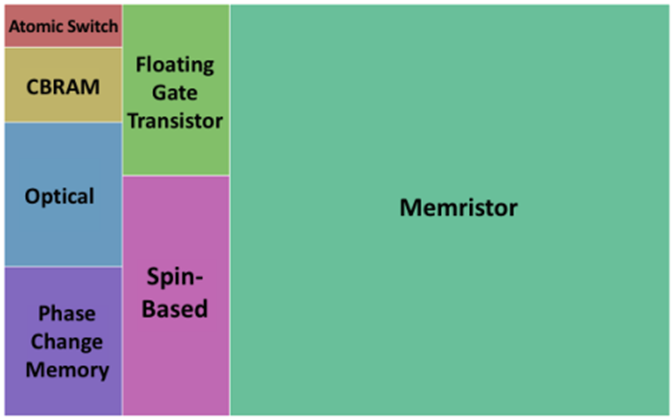

Các thành phần trong các hệ thống neuromorphic được thực hiện ở mức linh kiện được trình bày trong Hình 2.

i. Memristor

Có lẽ thành phần mức linh kiện phổ biến nhất trong các hệ thống neuromorphic là “điện trở bộ nhớ” hay còn gọi là memristor (memory resistor). Memristor là một phần tử mạch lý thuyết do Leon Chua đề xuất vào năm 1971 [25] và được các nhà nghiên cứu tại HP đưa ra vào năm 2008 [26]. Đặc điểm chính của linh kiện memristor là giá trị điện trở của nó phụ thuộc vào hoạt động trước của nó. Một trong những lý do chính mà các memristor trở nên phổ biến trong tính toán neuromorphic là mối quan hệ của chúng với các synapse; cụ thể là, các mạch kết hợp các memristor có thể biểu hiện hành vi giống-STDP rất tương tự như với những gì xảy ra trong các synapse sinh học. Trên thực tế, người ta đã đề xuất rằng STDP sinh học có thể được giải thích bằng memristance [27].

Các memristor có thể được làm từ nhiều loại vật liệu khác nhau, và những vật liệu khác nhau này có thể thể hiện những đặc tính hoàn toàn khác nhau. Một lý do khác để sử dụng các memristor trong các hệ thống neuromorphic là tiềm năng của chúng trong việc xây dựng năng lượng hiệu quả cho mạch điện, và điều này đã được nghiên cứu rộng rãi với một số công trình tập trung hoàn toàn vào việc đánh giá mức tiêu thụ năng lượng của mạch memristor trong các hệ thống neuromorphic [28]. Người ta cũng quan sát thấy rằng việc sử dụng các memristor cho triển khai neuromorphic là phù hợp vì khả năng chịu lỗi vốn có của các mô hình mạng nơ-ron có thể giúp giảm thiểu các tác động do sự thay đổi của linh kiện memristor gây ra [29].

Việc sử dụng phổ biến các memristor trong triển khai neuromorphic là một phần của hoặc toàn bộ quá trình triển khai synapse (tùy thuộc vào loại mạng). Đôi khi, memristor chỉ đơn giản được sử dụng như một phần tử lưu trữ trọng số synapse. Trong các trường hợp khác, do các đặc tính giống như tính dẻo của chúng, các memristor đã được sử dụng để triển khai các hệ thống synapse bao gồm học Hebbian tổng quát hoặc STDP nói riêng. Có lẽ cách sử dụng phổ biến nhất của một memristor trong các hệ thống neuromorphic là xây dựng một mảng thanh ngang (crossbar) của memristor để đại diện cho các synapse trong mạng [30, 31]. Các triển khai vật lý ban đầu của memristor đã nằm trong cấu hình mảng thanh ngang. Việc nhận ra mảng thanh ngang phổ biến trong tài liệu chủ yếu do lợi thế về mật độ của chúng cũng bởi vì mảng thanh ngang vật lý đã được chế tạo và cho thấy hoạt động tốt. Bởi vì một memristor đơn lẻ không thể đại diện cho các giá trị trọng số âm và dương cho một synapse, nên các synapse đa-memristor đã được đề xuất, bao gồm cả các synapse memristor bắc cầu vốn có thể nhận ra các giá trị trong số dương, âm và bằng không [32]. Do tính phổ biến tương đối của chúng trong các hệ thống neuromorphic, một tập hợp các thuật toán huấn luyện đã được phát triển đặc biệt với các đặc điểm của hệ thống memristor ghi nhớ, chẳng hạn như xử lý các đặc tính linh kiện không lý tưởng [33]. Memristor cũng đã được sử dụng để triển khai các sợi trục Hodgkin-Huxley trong phần cứng như một phần của quá trình thực hiện nơ-ron thần kinh [34].

Cần lưu ý rằng có rất nhiều vấn đề liên quan đến việc sử dụng các memristor để triển khai neuromorphic. Chúng bao gồm các vấn đề với đặc tính của memristor có thể ảnh hưởng nghiêm trọng đến hiệu suất của STDP và các biến thể hình học. Cũng cần lưu ý rằng một lượng lớn lý thuyết về mạng nơ-ron dùng memristor đã được thiết lập, bao gồm các tiêu chí về tính ổn định, tính đồng bộ hóa, và tính thụ động cho mạng nơ-ron dùng memristor. Tuy nhiên, những công việc này thường được thực hiện đối với các mô hình memristor lý tưởng và có thể không thực tế trong các hệ thống chế tạo.

ii. CBRAM và các công tắc nguyên tử

RAM cầu nối dẫn điện (Conductive-bridge RAM – CBRAM) cũng đã được sử dụng trong các hệ thống neuromorphic. Tương tự như RAM điện trở (Resistive RAM – ReRAM), được thực hiện bằng cách sử dụng các memristor dựa trên oxit kim loại hoặc vật liệu memristor, CBRAM là một công nghệ bộ nhớ không bay hơi (non-volatile). CBRAM đã được sử dụng để triển khai các synapse [35, 36] và tế bào thần kinh [37]. CBRAM khác với RAM điện trở ở chỗ nó sử dụng các đặc tính điện hóa để hình thành và hòa tan các kết nối. CBRAM nhanh, có kích thước nano và tiêu thụ điện năng rất thấp. Tương tự, công tắc nguyên tử (atomic switch) là linh kiện nano liên quan đến bộ nhớ điện trở hoặc memristor, điều khiển sự khuếch tán của các ion kim loại để tạo và phá hủy cầu nối nguyên tử giữa hai điện cực [38]. Công tắc nguyên tử đã được chế tạo cho các hệ thống neuromorphic. Các công tắc nguyên tử thường được sử dụng để thực hiện các synapse và đã được chứng minh là thực hiện tính dẻo của synapse theo cách tương tự như các phương pháp với các memristor [39].

Ngoài ra, một số loại linh kiện khác cũng được nghiên cứu sử dụng trong hệ thống neuromorphic như:

- Bộ nhớ thay đổi pha (Phase Change Memory)

- Linh kiện spin

- Transisor cực cổng thả nổi

- Quang học

Vật liệu cho các hệ thống Neuromorphic

Một trong những lĩnh vực phát triển quan trọng của tính toán neuromorphic trong những năm gần đây là chế tạo và mô tả đặc tính của vật liệu cho các hệ thống neuromorphic. Mặc dù chúng ta chủ yếu tập trung vào tính toán và các thành phần hệ thống của tính toán neuromorphic, nhưng cũng muốn nhấn mạnh sự đa dạng của các vật liệu mới và linh kiện kích thước nano đang được cộng đồng khoa học vật liệu chế tạo và rút trích đặc trưng cho các hệ thống neuromorphic.

Công tắc nguyên tử và CBRAM là hai trong số các linh kiện kích thước nano phổ biến được chế tạo bằng các vật liệu khác nhau có thể tạo ra các đặc trưng khác nhau. Vật liệu phổ biến cho công tắc nguyên tử là Ag2S, Ta2O5 và WO3 – x. Các vật liệu khác nhau cho công tắc nguyên tử có thể biểu diễn đặc trưng chuyển mạch khác nhau trong các điều kiện khác nhau. Do đó, việc lựa chọn vật liệu thích hợp có thể chi phối cách hoạt động của công tắc nguyên tử và có thể sẽ phụ thuộc vào ứng dụng. CBRAM đã được triển khai dùng GeS2/Ag, HfO2/GeS2, Cu/Ti/Al2O3, Ag/Ge0.3Se0.7, Ag2S và Cu/SiO2. Tương tự như các công tắc nguyên tử, đặc trưng chuyển mạch của linh kiện CBRAM cũng phụ thuộc vào vật liệu được chọn, độ ổn định và độ tin cậy của thiết bị cũng phụ thuộc vào vật liệu được chọn.

Có rất nhiều cách thực thi các memristor. Có lẽ cách triển khai memristor phổ biến nhất dựa trên các oxit kim loại chuyển tiếp. Đối với memristor oxit kim loại, nhiều loại vật liệu khác nhau được sử dụng, bao gồm HfOx, TiOx, WOx, SiOx, TaOx/TiOx, NiOx, TaOx, FeOx, AlOx, HfOx / ZnOx, và PCMO. Các loại memristor oxit kim loại khác nhau có thể tạo ra các con số và kiểu trạng thái điện trở khác nhau, điều này chi phối các giá trị trọng số có thể được “lưu trữ” trên memristor. Chúng cũng có các đặc tính về độ bền, độ ổn định và độ tin cậy khác nhau.

Một loạt các tài liệu khác dành cho memristor cũng đã được đề xuất. Ví dụ, các bộ nhớ mối nối đường hầm từ tính dựa trên spin trên MgO đã được đề xuất cho việc triển khai cả nơ-ron và synapse [40], mặc dù người ta đã lưu ý rằng chúng có một phạm vi giới hạn về các mức độ trở kháng khiến chúng ít được áp dụng để lưu trữ trọng số synapse. Chalcogenide memristor [41] cũng đã được sử dụng để thực hiện các synapse; một trong những lý do được đưa ra để sử dụng các memristor dựa trên chalcogenide là tốc độ chuyển đổi cực nhanh, cho phép các quá trình như STDP diễn ra ở mức nano giây. Các memristor dựa trên polyme đã được sử dụng vì chi phí thấp và hiệu suất có thể điều chỉnh được. Các memristor hữu cơ (bao gồm các polyme hữu cơ) cũng đã được đề xuất.

Vật liệu sắt điện (Ferroelectric) đã được xem xét để xây dựng bộ nhớ tương tự cho trọng số synapse [42] và linh kiện synapse [43], bao gồm cả những linh kiện dựa trên bộ nhớ ferroelectric. Các linh kiện chủ yếu được nghiên cứu là các linh kiện synapse 3 cực (trái ngược với các triển khai khác có thể là 2 cực). Linh kiện synapse 3 cực có thể nhận ra các quá trình học tập như STDP trong chính linh kiện [44], thay vì yêu cầu mạch bổ sung để thực hiện STDP.

Graphene gần đây đã được kết hợp trong các hệ thống neuromorphic để tạo ra các mạch nhỏ gọn hơn. Nó đã được sử dụng cho cả transistor [45] và điện trở [46] để thực hiện neuromorphic và trong các thực thi synapse đầy đủ [47].

Một vật liệu khác được xem xét cho một số triển khai neuromorphic là ống nano cacbon. Các ống nano carbon đã được đề xuất sử dụng trong nhiều thành phần neuromorphic khác nhau, bao gồm đuôi gai trên tế bào thần kinh [48], synapse [49], và tế bào thần kinh tăng vọt [50]. Lý do mà các ống nano carbon đã được sử dụng là chúng có thể tạo ra quy mô của hệ thống neuromorphic (số lượng tế bào thần kinh và synapse) và mật độ (theo synapse) có thể để giả lập hoặc mô phỏng các hệ thống neuromorphic. Chúng cũng đã được sử dụng để tương tác với mô sống, cho thấy rằng các hệ thống dựa trên ống nano carbon có thể hữu ích trong các ứng dụng giả của hệ thống neuromorphic.

Một loạt các transistor cho synapse cũng đã được chế tạo để thực hiện neuromorphic, bao gồm transistor synapse dựa trên silicon và transistor synapse dựa trên oxit. Các transistor điện hóa hữu cơ và transistor hạt nano hữu cơ cũng đã được sử dụng để xây dựng các thành phần neuromorphic như các synapse. Tương tự như các memristor hữu cơ, transistor hữu cơ đang được theo đuổi vì khả năng xử lý với chi phí thấp nhất và tính linh hoạt của chúng. Hơn nữa, chúng là tự nhiên để triển khai các giao tiếp não-máy (brain-machine) hoặc bất kỳ loại cảm biến hóa học hoặc sinh học nào.

Có rất nhiều nghiên cứu hứa hẹn trong lĩnh vực khoa học vật liệu để phát triển các linh kiện cho các hệ thống neuromorphic từ các vật liệu mới nhằm tạo ra các linh kiện neuromorphic nhỏ hơn, nhanh hơn và hiệu quả hơn.

Phần kết

Spiking Neural Network (SNN) hứa hẹn là mô hình mạng nơ-ron thế hệ kế tiếp có thể ứng dụng trong các lĩnh vực trí tuệ nhân tạo, máy tính thế hệ mới, y sinh học, mô phỏng não bộ, neuromorphic, v.v. Với các đặc tính gần với nơ-ron thần kinh sinh học, SNN tiêu thụ công suất thấp hơn, tính toán nhanh, khả năng thích nghi tốt. Các thành phần của mạng SNN bao gồm các nơ-ron, synapse, STDP có thể nghiên cứu và thực hiện từ mức vật lý, vật liệu, linh kiện điện tử đến mức mạch tương tự, mạch số và mức hệ thống trên chip, hứa hẹn nhiều dư địa để phát triển. Bên cạnh các hạn chế như: khả năng tự huấn luyện phức tạp, khó triển khai trên phần cứng, thiếu công cụ và nền tảng hỗ trợ, SNN vẫn đang thu hút sự quan tâm của các nhà khoa học, các start-up và các doanh nghiệp vì SNN có tiềm năng trong lĩnh vực AI sinh học, chip AI thế hệ mới, các hệ thống neuromorphic và các máy tính thế hệ mới.

Tác giả: PGS.TS. Lê Đức Hùng, Trường ĐH Khoa học tự nhiên, ĐH Quốc gia TP. HCM.

Biên tập: Quỹ Đổi mới sáng tạo Vingroup (VinIF).

TÀI LIỆU THAM KHẢO

[1] Schuman, Catherine & Potok, Thomas & Patton, Robert & Birdwell, J. & Dean, Mark & Rose, Garrett & Plank, James., “A Survey of Neuromorphic Computing and Neural Networks in Hardware”, arXiv:1705.06963, 2017.

[2] P. Richert, L. Spaanenburg, M. Kespert, J. Nijhuis, M. Schwarz, and A. Siggelkow, “ASICs for prototyping of pulse-density modulated neural networks,” VLSI design of neural networks, Springer, pp. 125–151, 1991.

[3] T. Schoenauer, N. Mehrtash, and H. Klar, “Architecture of a neuroprocessor chip for pulse-coded neural networks,” International Conference on Computational Intelligence and Neuroscience (ICCIN’98), pp. 17–20, 1998.

[4] F. Akopyan, J. Sawada, A. Cassidy, R. Alvarez-Icaza, J. Arthur, P. Merolla, N. Imam, Y. Nakamura, P. Datta, G.-J. Nam et al., “TRUENORTH: Design and tool flow of a 65mW 1 million neuron programmable neurosynaptic chip,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 34, No. 10, pp. 1537-1557, 2015.

[5] J. V. Arthur, P. A. Merolla, F. Akopyan, R. Alvarez, A. Cassidy, S. Chandra, S. K. Esser, N. Imam, W. Risk, D. B. D. Rubin et al., “Building block of a programmable neuromorphic substrate: A digital neurosynaptic core,” The 2012 International Joint Conference on Neural Networks (IJCNN), pp. 1–8, 2012.

[6] J.-S. Seo, B. Brezzo, Y. Liu, B. D. Parker, S. K. Esser, R. K. Montoye, B. Rajendran, J. A. Tierno, L. Chang, D. S. Modha et al., “A 45nm CMOS neuromorphic chip with a scalable architecture for learning in networks of spiking neurons,” Custom Integrated Circuits Conference (CICC), pp. 1–4, 2011.

[7] S. B. Furber, D. R. Lester, L. A. Plana, J. D. Garside, E. Painkras, S. Temple, and A. D. Brown, “Overview of the spinnaker system architecture,” IEEE Transactions on Computers, Vol. 62, Vo. 12, pp. 2454–2467, 2013.

[8] S. B. Furber, F. Galluppi, S. Temple, L. Plana et al., “The SpiNNaker project,” Proceedings of the IEEE, vol. 102, no. 5, pp. 652–665, 2014.

[9] S. Furber, “Large-scale neuromorphic computing systems,” Journal of Neural Engineering, Vol. 13, No. 5, p. 051001, 2016.

[10] P. Rocke, B. McGinley, J. Maher, F. Morgan, and J. Harkin, “Investigating the suitability of FPAAs for evolved hardware spiking neural networks,” Evolvable Systems: From Biology to Hardware, Springer, pp. 118–129, 2008.

[11] P. Dong, G. L. Bilbro, and M.-Y. Chow, “Implementation of artificial neural network for real time applications using field programmable analog arrays,” in Neural Networks, 2006. IJCNN’06. International Joint Conference on. IEEE, 2006, pp. 1518–1524.

[12] E. Farquhar, C. Gordon, and P. Hasler, “A Field Programmable Neural Array,” IEEE International Symposium on Circuits and Systems (ISCAS 2006), pp. 1–4, 2006.

[13] M. Liu, H. Yu, and W. Wang, “FPAA based on integration of CMOS and nanojunction devices for neuromorphic applications,” NanoNet, Springer, pp. 44–48, 2009.

[14] C. Mead, “Neuromorphic Electronic Systems,” Proceedings of the IEEE, Vol. 78, No. 10, pp. 1629–1636, 1990.

[15] L. Alvado, J. Tomas, R.-L. Masson, V. Douence et al., “Design of an analogue asic using subthreshold cmos transistors to model biological neurons,” IEEE Conference on Custom Integrated Circuits, pp. 97–100, 2001.

[16] G. Indiveri and G. Bisio, “Analog subthreshold vlsi implementation of a neuromorphic model of the visual cortex for pre-attentive vision,” The Fourth International Conference on Microelectronics for Neural Networks and Fuzzy Systems, pp. 439–448, 1994.

[17] R. H. Hahnloser, R. Sarpeshkar, M. A. Mahowald, R. J. Douglas, and H. S. Seung, “Digital selection and analogue amplification coexist in a cortex-inspired silicon circuit,” Nature, Vol. 405, No. 6789, pp. 947–951, 2000.

[18] T. Zahn, R. Izak, and K. Trott, “Mixed analog-digital neurochip for acoustical attention,” Graduiertenkolleg “Informatik und Technik”, TU Ilmenau, 1996.

[19] G. Charles, C. Gordon, and W. E. Alexander, “An implementation of a biological neural model using analog-digital integrated circuits,” IEEE Internatio nal Behavioral Modeling and Simulation Workshop, (BMAS 2008), pp. 78–83, 2008.

[20] M. DeYong, R. L. Findley, and C. Fields, “The design, fabrication, and test of a new VLSI hybrid analog-digital neural processing element,” IEEE Transactions on Neural Networks, Vol. 3, No. 3, pp. 363–374, 1992.

[21] V. Douence, S. Renaud-Le Masson, S. Saighi, and G. Le Masson, “A field-programmable conductance array IC for biological neurons modeling,” Bio-Inspired Applications of Connectionism, Springe, pp. 31–38, 2001.

[22] B. W. Lee and B. Sheu, “A compact and general-purpose neural chip with electrically programmable synapses,” IEEE Custom Integrated Circuits Conference, pp. 26.6.1-26.6.4, 1990.

[23] B. V. Benjamin, P. Gao, E. McQuinn, S. Choudhary, A. R. Chandrasekaran, J. Bussat, R. Alvarez-Icaza, J. V. Arthur, P. A. Merolla, and K. Boahen, “Neurogrid: A mixed-analog-digital multichip system for large-scale neural simulations,” Proceedings of the IEEE, Vol. 102, No. 5, pp. 699–716, 2014.

[24] J. Schemmel, A. Grubl, S. Hartmann, A. Kononov, C. Mayr, K. Meier, S. Millner, J. Partzsch, S. Schiefer, S. Scholze et al., “Live demonstration: A scaled-down version of the brainscales wafer-scale neuromorphic system,” IEEE International Symposium on Circuits and Systems (ISCAS 2012), pp. 702–702, 2012.

[25] L. Chua, “Memristor-the missing circuit element,” IEEE Transactions on Circuit Theory, Vol. 18, No. 5, pp. 507–519, 1971.

[26] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, “The missing memristor found,” Nature, Vol. 453, No. 7191, pp. 80–83, 2008.

[27] B. Linares-Barranco and T. Serrano-Gotarredona, “Memristance can explain spike-time-dependent-plasticity in neural synapses,” Nature precedings, Vol. 1, p. 2009, 2009.

[28] L. Deng, D. Wang, Z. Zhang, P. Tang, G. Li, and J. Pei, “Energy consumption analysis for various memristive networks under different learning strategies,” Physics Letters A, Vol. 380, No. 7, pp. 903–909, 2016.

[29] D. Querlioz, O. Bichler, and C. Gamrat, “Simulation of a memristorbased spiking neural network immune to device variations,” The 2011 International Joint Conference on Neural Networks (IJCNN), pp. 1775–1781, 2011.

[30] G. C. Adam, B. D. Hoskins, M. Prezioso, F. Merrikh-Bayat, B. Chakrabarti, and D. B. Strukov, “3-D memristor crossbars for analog and neuromorphic computing applications,” IEEE Transactions on Electron Devices, Vol. 64, No. 1, pp. 312–318, 2017.

[31] I. Kataeva, F. Merrikh-Bayat, E. Zamanidoost, and D. Strukov, “Efficient training algorithms for neural networks based on memristive crossbar circuits,” 2015 International Joint Conference on Neural Networks (IJCNN), pp. 1–8, 2015.

[32] S. P. Adhikari, C. Yang, H. Kim, and L. O. Chua, “Memristor bridge synapse-based neural network and its learning,” IEEE Transactions on Neural Networks and Learning Systems, Vol. 23, No. 9, pp. 1426–1435, 2012.

[33] M. Al-Shedivat, R. Naous, E. Neftci, G. Cauwenberghs, and K. N. Salama, “Inherently stochastic spiking neurons for probabilistic neural computation,” The 7th International IEEE/EMBS Conference on Neural Engineering (NER), pp. 356–359, 2015.

[34] M. S. Feali and A. Ahmadi, “Realistic Hodgkin–Huxley axons using stochastic behavior of memristors,” Neural Processing Letters, pp. 1–14, 2016.

[35] B. DeSalvo, E. Vianello, D. Garbin, O. Bichler, and L. Perniola, “From memory in our brain to emerging resistive memories in neuromorphic systems,” 2015 IEEE International Memory Workshop (IMW), pp. 1–4, 2015.

[36] D. Roclin, O. Bichler, C. Gamrat, and J.-O. Klein, “Sneak paths effects in CBRAM memristive devices arrays for spiking neural networks,” 2014 IEEE/ACM International Symposium on Nanoscale Architectures, pp. 13–18, 2014.

[37] J. W. Jang, B. Attarimashalkoubeh, A. Prakash, H. Hwang, and Y. H. Jeong, “Scalable Neuron Circuit Using Conductive-Bridge RAM for Pattern Reconstructions,” IEEE Transactions on Electron Devices, Vol. 63, No. 6, pp. 2610-2613, 2016.

[38] M. Aono and T. Hasegawa, “The Atomic Switch,” Proceedings of the IEEE, Vol. 98, No. 12, pp. 2228–2236, 2010.

[39] A. V. Avizienis, H. O. Sillin, C. Martin-Olmos, H. H. Shieh, M. Aono, A. Z. Stieg, and J. K. Gimzewski, “Neuromorphic atomic switch networks,” PLOS One, Vol. 7, No. 8, e42772, pp. 1-8, 2012.

[40] P. Krzysteczko, J. Munchenberger, M. Schoafers, G. Reiss, and A. Thomas, “The memristive magnetic tunnel junction as a nanoscopic synapse-neuron system,” Advanced Materials, Vol. 24, No. 6, pp. 762–766, 2012.

[41] Y. Li, Y. Zhong, L. Xu, J. Zhang, X. Xu, H. Sun, and X. Miao, “Ultrafast Synaptic Events in a Chalcogenide Memristor,” Scientific Reports, Vol. 3, 1619, pp. 1-7, 2013.

[42] H. Ishiwara, “Proposal of Adaptive-Learning Neuron Circuits with Ferroelectric Analog-Memory Weights,” Japanese Journal of Applied Physics, Vol. 32, No. 1S, p. 442, 1993.

[43] E. Kim, K. Kim, and S. Yoon, “Investigation of the ferroelectric switching behavior of P (VDF-TrFE)-PMMA blended films for synaptic device applications,” Journal of Physics D: Applied Physics, Vol. 49, No. 7, p. 075105, 2016.

[44] Y. Nishitani, Y. Kaneko, M. Ueda, T. Morie, and E. Fujii, “Threeterminal ferroelectric synapse device with concurrent learning function for artificial neural networks,” Journal of Applied Physics, Vol. 111, No. 12, p. 124108, 2012.

[45] C. J. Wan, Y. H. Liu, P. Feng, W. Wang, L. Q. Zhu, Z. P. Liu, Y. Shi, and Q. Wan, “Flexible Metal Oxide/Graphene Oxide Hybrid Neuromorphic Transistors on Flexible Conducting Graphene Substrates,” Advanced Materials, pp. 1-27, 2016.

[46] M. Darwish, V. Calayir, L. Pileggi, and J. Weldon, “Ultra-compact Graphene Multigate Variable Resistor For Neuromorphic Computing,” IEEE Transactions on Nanotechnology, Vol. 15, No. 2, pp. 318-327, 2016.

[47] H. Tian, W. Mi, X.-F. Wang, H. Zhao, Q.-Y. Xie, C. Li, Y.-X. Li, Y. Yang, and T.-L. Ren, “Graphene Dynamic Synapse with Modulatable Plasticity,” Nano Letters, Vol. 15, No. 12, pp. 8013–8019, 2015.

[48] J. Joshi, C. Hsu, A. C. Parker, and P. Deshmukh, “A Carbon Nanotube Cortical Neuron with Excitatory and Inhibitory Dendritic Computations,” IEEE/NIH LIfe Science Systems and Applications Workshop, pp. 133-136, 2009.

[49] K. Gacem, J.-M. Retrouvey, D. Chabi, A. Filoramo, W. Zhao, J.-O. Klein, and V. Derycke, “Neuromorphic Function Learning with Carbon Nanotube Based Synapses,” Nanotechnology, Vol. 24, No. 38, p. 384013, 2013.

[50] J. Joshi, A. Parker, and C. Hsu, “A Carbon Nanotube Spiking Cortical Neuron with Tunable Refractory Period and Spiking Duration,” IEEE Latin American Symp. on Circuits and Systems (LASCAS), pp. 97-100, 2010.